6.1 Uvod

Sodobni računalniki za splošno uporabo so dveh vrst: CISC in RISC. CISC je kratica za Complex Instruction Set Computer. RISK je kratica za Reduced Instruction Set Computer. Mikroprocesorji 6502 ali 6510, kot veljajo za računalnik Commodore-64, bolj spominjajo na arhitekturo RISC kot na arhitekturo CISC.

Računalniki RISC imajo na splošno krajša navodila v zbirnem jeziku (po številu bajtov) v primerjavi z računalniki CISC.

Opomba : Ne glede na to, ali gre za CISC, RISC ali stari računalnik, se periferna naprava začne z notranjimi vrati in gre navzven skozi zunanja vrata na navpični površini sistemske enote računalnika (osnovne enote) in do zunanje naprave.

Tipično navodilo računalnika CISC je mogoče razumeti kot združevanje več kratkih ukazov zbirnega jezika v eno daljše navodilo zbirnega jezika, zaradi česar je nastalo navodilo zapleteno. Zlasti računalnik CISC naloži operande iz pomnilnika v mikroprocesorske registre, izvede operacijo in nato shrani rezultat nazaj v pomnilnik, vse v enem ukazu. Po drugi strani pa so to vsaj tri navodila (kratka) za računalnik RISC.

Obstajata dve priljubljeni seriji računalnikov CISC: mikroprocesorski računalniki Intel in mikroprocesorski računalniki AMD. AMD pomeni Advanced Micro Devices; je podjetje za proizvodnjo polprevodnikov. Intelove serije mikroprocesorjev po vrstnem redu razvoja so 8086, 8088, 80186, 80286, 80386, 80486, Pentium, Core, i Series, Celeron in Xeon. Navodila zbirnega jezika za zgodnje intelove mikroprocesorje, kot sta 8086 in 8088, niso zelo zapletena. Vendar so za nove mikroprocesorje zapleteni. Najnovejši mikroprocesorji AMD za serijo CISC so Ryzen, Opteron, Athlon, Turion, Phenom in Sempron. Mikroprocesorji Intel in AMD so znani kot mikroprocesorji x86.

ARM pomeni Advanced RISC Machine. Arhitekture ARM definirajo družino procesorjev RISC, ki so primerni za uporabo v najrazličnejših aplikacijah. Medtem ko se številni mikroprocesorji Intel in AMD uporabljajo v namiznih osebnih računalnikih, številni procesorji ARM služijo kot vgrajeni procesorji v sistemih, ki so pomembni za varnost, kot so avtomobilski sistemi proti blokiranju koles, in kot procesorji za splošno uporabo v pametnih urah, prenosnih telefonih, tablicah in prenosnih računalnikih. . Čeprav lahko obe vrsti mikroprocesorjev vidimo v majhnih in velikih napravah, mikroprocesorje RISC najdemo bolj v majhnih kot v velikih napravah.

Računalniška beseda

Če za računalnik rečemo, da je računalnik z 32-bitno besedo, to pomeni, da se informacije shranjujejo, prenašajo in manipulirajo v obliki dvaintrideset-bitnih binarnih kod znotraj notranjega dela matične plošče. Pomeni tudi, da so splošni registri v mikroprocesorju računalnika široki 32 bitov. Registri A, X in Y mikroprocesorja 6502 so registri splošnega namena. Široki so osem bitov, zato je računalnik Commodore-64 osembitni besedni računalnik.

Nekaj besednega zaklada

Računalniki X86

Pomeni bajta, besede, dvojne besede, štiribesede in dvojne štiribesede so za računalnike x86 naslednji:

- Bajt : 8 bitov

- Beseda : 16 bitov

- Dvojna beseda : 32 bitov

- štiribeseda : 64 bitov

- Dvojna štiribeseda : 128 bitov

Računalniki ARM

Pomeni bajta, polbesede, besede in dvojne besede so za računalnike ARM naslednji:

- Bajt : 8 bitov

- Postanite pol : 16 bitov

- Beseda : 32 bitov

- Dvojna beseda : 64 bitov

Upoštevati je treba razlike in podobnosti imen (in vrednosti) x86 in ARM.

Opomba : Predznačna cela števila v obeh vrstah računalnikov so komplement dveh.

Lokacija pomnilnika

Pri računalniku Commodore-64 je pomnilniška lokacija običajno en bajt, vendar je občasno lahko dva zaporedna bajta, če upoštevamo kazalce (posredno naslavljanje). Pri sodobnem računalniku x86 je pomnilniška lokacija 16 zaporednih bajtov, ko imamo opravka z dvojno štiribesedo 16 bajtov (128 bitov), 8 zaporednih bajtov, ko imamo opravka s štiribesedo 8 bajtov (64 bitov), 4 zaporedne bajte, ko imamo opravka z dvojno besedo 4 bajti (32 bitov), 2 zaporedna bajta, ko imamo opravka z besedo 2 bajtov (16 bitov), in 1 bajt, ko imamo opravka z bajtom (8 bitov). Pri sodobnem računalniku ARM je pomnilniška lokacija 8 zaporednih bajtov, ko imamo opravka z dvojno besedo 8 bajtov (64 bitov), 4 zaporedne bajte, ko imamo opravka z besedo 4 bajtov (32 bitov), 2 zaporedna bajta, ko imamo opravka s polbesedo 2 bajta (16 bitov) in 1 bajt, ko imamo opravka z bajtom (8 bitov).

V tem poglavju je razloženo, kaj je skupnega v arhitekturah CISC in RISC in kakšne so njune razlike. To se izvede v primerjavi z računalnikom 6502 µP in računalnikom commodore-64, kjer je to primerno.

6.2 Blokovni diagram matične plošče sodobnega osebnega računalnika

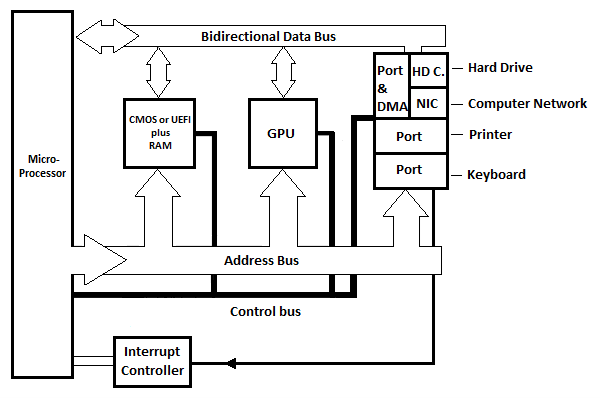

PC pomeni osebni računalnik. Sledi generični osnovni blokovni diagram za sodobno matično ploščo z enim mikroprocesorjem za osebni računalnik. Predstavlja matično ploščo CISC ali RISC.

Slika 6.21 Osnovni blokovni diagram matične plošče sodobnega osebnega računalnika

Na diagramu so prikazana tri notranja vrata, v praksi pa jih je več. Vsaka vrata imajo register, ki ga lahko vidimo kot vrata sama. Vsako vezje vrat ima vsaj še en register, ki ga lahko imenujemo 'statusni register'. Statusni register označuje vrata do programa, ki pošilja prekinitveni signal mikroprocesorju. Obstaja vezje krmilnika prekinitev (ni prikazano), ki razlikuje med različnimi prekinitvenimi linijami iz različnih vrat in ima le nekaj linij do µP.

HD.C v diagramu pomeni kartico trdega diska. NIC pomeni omrežno vmesniško kartico. Kartica trdega diska (vezje) je povezana s trdim diskom, ki je znotraj osnovne enote (sistemske enote) sodobnega računalnika. Omrežna vmesniška kartica (vezje) je prek zunanjega kabla povezana z drugim računalnikom. Na diagramu so ena vrata in DMA (glejte naslednjo sliko), ki sta povezana s kartico trdega diska in/ali z omrežno vmesniško kartico. DMA pomeni neposredni dostop do pomnilnika.

Ne pozabite iz poglavja o računalniku Commodore-64, da je treba za pošiljanje bajtov iz pomnilnika na diskovni pogon ali drug računalnik vsak bajt kopirati v register v mikroprocesorju, preden se kopira v ustrezna notranja vrata, in nato samodejno na napravo. Za sprejem bajtov z diskovnega pogona ali drugega računalnika v pomnilnik je treba vsak bajt prekopirati iz ustreznega registra notranjih vrat v register mikroprocesorja, preden se kopira v pomnilnik. To običajno traja dolgo, če je število bajtov v toku veliko. Rešitev za hiter prenos je uporaba neposrednega dostopa do pomnilnika (vezja) brez prehoda skozi mikroprocesor.

Vezje DMA je med vrati in HD. C ali NIC. Z neposrednim dostopom do pomnilnika vezja DMA poteka prenos velikih tokov bajtov neposredno med vezjem DMA in pomnilnikom (RAM) brez nadaljnjega sodelovanja mikroprocesorja. DMA uporablja naslovno vodilo in podatkovno vodilo namesto µP. Skupno trajanje prenosa je krajše, kot če bi uporabili µP hard. Tako HD C. kot NIC uporabljata DMA, ko imata velik tok podatkov (bajtov) za prenos z RAM-om (pomnilnikom).

GPU je kratica za grafično procesno enoto. Ta blok na matični plošči je odgovoren za pošiljanje besedila in gibljivih ali mirujočih slik na zaslon.

Pri sodobnih računalnikih (PC) ni pomnilnika samo za branje (ROM). Obstaja pa BIOS ali UEFI, ki je neke vrste obstojni RAM. Podatke v BIOS-u dejansko vzdržuje baterija. Baterija je tisto, kar dejansko vzdržuje tudi časovnik ure ob pravem času in datumu za računalnik. UEFI je bil izumljen po BIOS-u in je nadomestil BIOS, čeprav je BIOS še vedno zelo pomemben v sodobnih osebnih računalnikih. O tem bomo več razpravljali pozneje!

V sodobnih osebnih računalnikih naslovna in podatkovna vodila med µP in vezji notranjih vrat (in pomnilnikom) niso vzporedna vodila. So serijska vodila, ki potrebujejo dva vodnika za prenos v eno smer in še dva vodnika za prenos v nasprotni smeri. To na primer pomeni, da je 32-bitov mogoče poslati zaporedno (en bit za drugim) v obe smeri.

Če je serijski prenos samo v eni smeri z dvema vodnikoma (dvema linijama), je to poldupleksni prenos. Če je serijski prenos v obe smeri s štirimi prevodniki, enim parom v obe smeri, se to imenuje polni dupleks.

Celoten pomnilnik sodobnega računalnika je še vedno sestavljen iz niza lokacij bajtov: osem bitov na bajt. Sodoben računalnik ima pomnilniški prostor vsaj 4 gigabajtov = 4 x 210 x 2 10 x 2 10 = 4 x 1.073.741.824 10 bajtov = 4 x 1024 10/pod> x 1024 10 x 1024 10 = 4 x 1.073.741.824 10 .

Opomba : Čeprav na prejšnji matični plošči ni prikazano vezje časovnika, imajo vse sodobne matične plošče vezja časovnika.

6.3 Osnove računalniške arhitekture x64

6.31 Nabor registrov x64

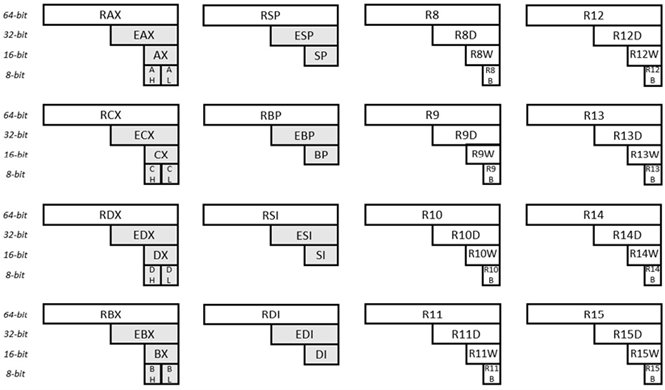

64-bitni mikroprocesor iz serije mikroprocesorjev x86 je 64-bitni mikroprocesor. Precej moderno je nadomestiti 32-bitni procesor iste serije. Splošni registri 64-bitnega mikroprocesorja in njihova imena so naslednja:

Slika 6.31 Splošni registri za x64

Na dani sliki je prikazanih šestnajst (16) splošnih registrov. Vsak od teh registrov je širok 64 bitov. Če pogledamo register v zgornjem levem kotu, je 64 bitov identificiranih kot RAX. Prvih 32 bitov tega istega registra (z desne) je identificiranih kot EAX. Prvih 16 bitov tega istega registra (z desne) je identificiranih kot AX. Drugi bajt (z desne) tega istega registra je identificiran kot AH (H tukaj pomeni visoko). In prvi bajt (tega istega registra) je identificiran kot AL (L tukaj pomeni nizek). Če pogledamo register v spodnjem desnem kotu, je 64 bitov identificiranih kot R15. Prvih 32 bitov tega istega registra je identificiranih kot R15D. Prvih 16 bitov tega istega registra je identificiranih kot R15W. In prvi bajt je identificiran kot R15B. Podobno so razložena tudi imena ostalih registrov (in podregistrov).

Obstaja nekaj razlik med Intel in AMD µP. Informacije v tem razdelku so za Intel.

Pri 6502 µP je register programskega števca (ni neposredno dostopen), ki vsebuje naslednji ukaz, ki ga je treba izvesti, širok 16 bitov. Tukaj (x64) se programski števec imenuje Instruction Pointer in je širok 64 bitov. Označen je kot RIP. To pomeni, da lahko x64 µP naslovi do 264 = 1,844674407 x 1019 (dejansko 18.446.744.073.709.551.616) lokacij pomnilniških bajtov. RIP ni register za splošne namene.

Stack Pointer Register ali RSP je med 16 registri splošnega namena. Kaže na zadnji vnos sklada v pomnilniku. Tako kot pri 6502 µP sklad za x64 raste navzdol. Pri x64 se sklad v RAM-u uporablja za shranjevanje povratnih naslovov za podprograme. Uporablja se tudi za shranjevanje 'senčnega prostora' (glejte naslednjo razpravo).

6502 µP ima 8-bitni register stanja procesorja. Ekvivalent v x64 se imenuje register RFLAGS. Ta register shranjuje zastavice, ki se uporabljajo za rezultate operacij in za krmiljenje procesorja (µP). Širok je 64 bitov. Višjih 32 bitov je rezerviranih in se trenutno ne uporabljajo. Naslednja tabela podaja imena, indekse in pomene pogosto uporabljenih bitov v registru RFLAGS:

| Tabela 6.31.1 Najpogosteje uporabljene zastavice RFLAGS (biti) |

|||

|---|---|---|---|

| Simbol | bit | Ime | Namen |

| CF | 0 | Nositi | Nastavi se, če aritmetična operacija ustvari prenos ali izposojo iz najpomembnejšega bita rezultata; drugače očiščeno. Ta zastavica označuje pogoj prelivanja za aritmetiko celih števil brez predznaka. Uporablja se tudi v aritmetiki z večkratno natančnostjo. |

| PF | 2 | Pariteta | Nastavi se, če najmanjši bajt rezultata vsebuje sodo število 1 bitov; drugače očiščeno. |

| OF | 4 | Prilagodi | Nastavljena je, če aritmetična operacija ustvari prenos ali izposojo iz bita 3 rezultata; drugače očiščeno. Ta zastavica se uporablja v binarno kodirani decimalni (BCD) aritmetiki. |

| ZF | 6 | Nič | Nastavi se, če je rezultat nič; drugače očiščeno. |

| SF | 7 | Podpis | Nastavljena je, če je enaka najpomembnejšemu bitu rezultata, ki je bit predznaka predznačenega celega števila (0 označuje pozitivno vrednost in 1 označuje negativno vrednost). |

| OF | enajst | Preliv | Nastavi se, če je celoštevilski rezultat preveliko pozitivno število ali premajhno negativno število (razen predznakovnega bita), da bi se prilegal ciljnemu operandu; drugače očiščeno. Ta zastavica označuje pogoj prelivanja za aritmetiko celega števila s predznakom (komplement dveh). |

| DF | 10 | Smer | Nastavljeno je, če delujejo ukazi niza smeri (inkrement ali dekrement). |

| ID | enaindvajset | Identifikacija | Nastavljen je, če spremenljivost označuje prisotnost ukaza CPUID. |

Poleg osemnajstih 64-bitnih registrov, ki so bili prej navedeni, ima arhitektura x64 µP osem 80-bitnih širokih registrov za aritmetiko s plavajočo vejico. Teh osem registrov je mogoče uporabiti tudi kot registre MMX (glejte naslednjo razpravo). Obstaja tudi šestnajst 128-bitnih registrov za XMM (glejte naslednjo razpravo).

To ni vse o registrih. Obstaja več registrov x64, ki so segmentni registri (večinoma neuporabljeni v x64), nadzorni registri, registri za upravljanje pomnilnika, registri za odpravljanje napak, registri za virtualizacijo, registri zmogljivosti, ki sledijo vsem vrstam notranjih parametrov (zadetki/zgrešitve predpomnilnika, izvedene mikro operacije, časovni razpored , in veliko več).

SIMD

SIMD pomeni Single Instruction Multiple Data. To pomeni, da lahko en ukaz zbirnega jezika deluje na več podatkih hkrati v enem mikroprocesorju. Razmislite o naslednji tabeli:

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | |

| + | 9 | 10 | enajst | 12 | 13 | 14 | petnajst | 16 |

| = | 10 | 12 | 14 | 16 | 18 | dvajset | 22 | 24 |

V tej tabeli je vzporedno dodanih osem parov števil (v enakem trajanju), da dobimo osem odgovorov. Eno navodilo zbirnega jezika lahko izvede osem vzporednih seštevanj celih števil v registrih MMX. Podobno je mogoče narediti z registri XMM. Torej obstajajo navodila MMX za cela števila in navodila XMM za števila s plavajočim.

6.32 Zemljevid pomnilnika in x64

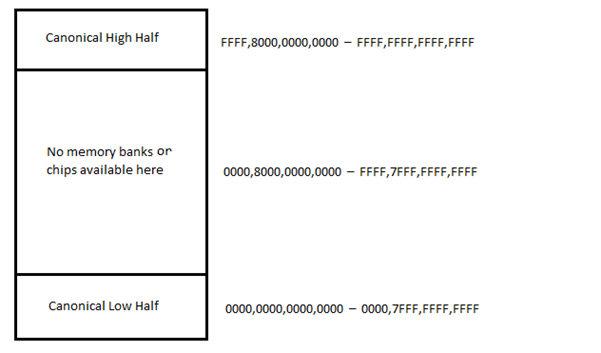

S kazalcem ukazov (programski števec), ki ima 64 bitov, to pomeni, da je mogoče nasloviti 264 = 1,844674407 x 1019 lokacij pomnilniških bajtov. V šestnajstiškem sistemu je lokacija najvišjega bajta FFFF,FFFF,FFFF,FFFF16. Noben običajni računalnik danes ne more zagotoviti tako velikega pomnilniškega (popolnega) prostora. Primerna pomnilniška karta za računalnik x64 je torej naslednja:

Upoštevajte, da vrzel od 0000,8000,0000,000016 do FFFF,7FFF,FFFF,FFFF16 nima pomnilniških lokacij (brez pomnilniških bank RAM). To je razlika FFFF,0000,0000,000116, ki je precej velika. Kanonična visoka polovica ima operacijski sistem, kanonična spodnja polovica pa uporabniške programe (aplikacije) in podatke. Operacijski sistem je sestavljen iz dveh delov: majhnega UEFI (BIOS) in velikega dela, ki se naloži s trdega diska. Naslednje poglavje govori več o sodobnih operacijskih sistemih. Upoštevajte podobnost s to pomnilniško karto in tisto za Commodore-64, ko je 64 KB morda izgledalo kot veliko pomnilnika.

V tem kontekstu se operacijski sistem grobo imenuje 'jedro'. Jedro je podobno jedru računalnika Commodore-64, vendar ima veliko več podprogramov.

Endianness za x64 je little endian, kar pomeni, da za lokacijo nižji naslov kaže na nižji bajt vsebine v pomnilniku.

6.33 Načini naslavljanja zbirnega jezika za x64

Načini naslavljanja so načini, kako lahko navodilo dostopa do registrov µP in pomnilnika (vključno z registri notranjih vrat). x64 ima veliko načinov naslavljanja, vendar so tukaj obravnavani samo pogosto uporabljeni načini naslavljanja. Splošna sintaksa za navodila tukaj je:

opcode destinacija, vir

Decimalna števila so zapisana brez predpone ali pripone. Pri 6502 je vir impliciten. x64 ima več operacijskih kod kot 6502, vendar imajo nekatere operacijske kode enako mnemoniko. Posamezna navodila x64 so spremenljive dolžine in lahko obsegajo od 1 do 15 bajtov. Pogosto uporabljeni načini naslavljanja so naslednji:

Način takojšnjega naslavljanja

Tu je izvorni operand dejanska vrednost in ne naslov ali oznaka. Primer (preberi komentar):

DODAJ EAX, 14 ; dodajte decimalno 14 v 32-bitni EAX od 64-bitnega RAX, odgovor ostane v EAX (cilj)

Registrirajte se za način registracije naslavljanja

primer:

DODAJ R8B, AL ; dodajte 8-bitni AL RAX v R8B 64-bitnega R8 – odgovori ostanejo v R8B (cilj)

Način posrednega in indeksiranega naslavljanja

Posredno naslavljanje s 6502 µP pomeni, da ima lokacija danega naslova v navodilu efektivni naslov (kazalec) končne lokacije. Podobno se zgodi z x64. Indeksno naslavljanje s 6502 µP pomeni, da je vsebina registra µP dodana podanemu naslovu v navodilu, da dobimo učinkovit naslov. Podobno se dogaja pri x64. Poleg tega je pri x64 vsebino registra mogoče pomnožiti z 1 ali 2 ali 4 ali 8, preden se doda danemu naslovu. Ukaz mov (kopiranje) x64 lahko združuje posredno in indeksirano naslavljanje. primer:

MOV R8W, 1234[8*RAX+RCX] ; premakni besedo na naslov (8 x RAX + RCX) + 1234

Tukaj ima R8W prvih 16 bitov R8. Podani naslov je 1234. Register RAX ima 64-bitno številko, ki je pomnožena z 8. Rezultat se doda vsebini 64-bitnega registra RCX. Ta drugi rezultat se doda danemu naslovu, ki je 1234, da se pridobi dejanski naslov. Številka na mestu dejanskega naslova se premakne (kopira) na prvo 16-bitno mesto (R8W) registra R8 in nadomesti tisto, kar je tam. Bodite pozorni na uporabo oglatih oklepajev. Ne pozabite, da je beseda v x64 široka 16 bitov.

Relativno naslavljanje RIP

Za 6502 µP se relativno naslavljanje uporablja samo z navodili za razvejanje. Tam je en sam operand operacijske kode odmik, ki se doda ali odšteje od vsebine programskega števca za efektivni naslov ukaza (ne naslov podatkov). Podobno se zgodi pri x64, kjer se programski števec imenuje kot kazalec ukazov. Navodilo z x64 ne sme biti samo navodilo za razvejanje. Primer RIP-relativnega naslavljanja je:

MOV AL, [RIP]

AL of RAX ima 8-bitno številko s predznakom, ki se doda ali odšteje od vsebine v RIP (64-bitni kazalec navodil), da kaže na naslednje navodilo. Upoštevajte, da sta izvor in cilj v tem navodilu izjemoma zamenjana. Upoštevajte tudi uporabo oglatih oklepajev, ki se nanašajo na vsebino RIP.

6.34 Pogosto uporabljena navodila za x64

V naslednji tabeli * pomeni različne možne pripone podnabora operacijskih kod:

| Tabela 6.34.1 Pogosto uporabljena navodila v x64 |

|

|---|---|

| Opcode | Pomen |

| MOV | Premik (kopiranje) v/iz/med pomnilnikom in registri |

| CMOV* | Različne pogojne poteze |

| XCHG | Menjava |

| BSWAP | Zamenjava bajtov |

| PUSH/POP | Uporaba sklada |

| ADD/ADC | Dodaj/s prenosom |

| SUB/SBC | Odštej/s prenašanjem |

| MUL/IMUL | Pomnoži/nepredznačeno |

| DIV/IDIV | Razdeli/nepredznačeno |

| VKLJ./PAD | Povečanje/Zmanjšanje |

| NEG | Negiraj |

| CMP | Primerjaj |

| IN/ALI/XALI/NE | Bitne operacije |

| SHR/SAR | Premik desno logično/aritmetično |

| SHL/SAL | Premik levo logično/aritmetično |

| ROR/VLOGA | Zavrtite desno/levo |

| RCR/RCL | Zavrtite desno/levo skozi nosilec |

| BT/BTS/BTR | Test bitov/in nastavitev/in ponastavitev |

| JMP | Brezpogojni skok |

| JE/JNE/JC/JNC/J* | Skoči, če je enako/ni enako/nosi/ne nosi/mnogi drugi |

| HODI/HODI/HODI | Zanka z ECX |

| KLIC/POVN | Pokliči podprogram/vrnitev |

| NOP | Brez operacije |

| CPUID | informacije o procesorju |

x64 ima navodila za množenje in deljenje. V svojem µP ima strojna vezja za množenje in deljenje. 6502 µP nima strojnih vezij za množenje in deljenje. Množenje in deljenje je hitreje opraviti strojno kot programsko (vključno s premikanjem bitov).

Navodila za niz

Obstaja veliko nizovnih ukazov, vendar je edino, o katerem bomo tukaj razpravljali, MOVS (za premikanje niza) navodilo za kopiranje niza, ki se začne na naslovu C000 H . Za začetek na naslovu C100 H , uporabite naslednja navodila:

MOVS [C100H], [C000H]

Upoštevajte pripono H za šestnajstiško.

6.35 Zanka v x64

6502 µP ima navodila za razvejanje za zanko. Navodilo za razvejanje skoči na lokacijo naslova, ki ima novo navodilo. Lokacija naslova se lahko imenuje 'zanka'. x64 ima navodila LOOP/LOOPE/LOOPNE za zanko. Teh rezerviranih besed zbirnega jezika ne smete zamenjevati z oznako 'zanke' (brez narekovajev). Obnašanje je naslednje:

LOOP zmanjša ECX in preveri, ali ECX ni nič. Če je ta pogoj (nič) izpolnjen, skoči na določeno oznako. V nasprotnem primeru pade (nadaljujte z ostalimi navodili v naslednji razpravi).

LOOPE zmanjša ECX in preveri, ali ECX ni nič (lahko je na primer 1) in je ZF nastavljen (na 1). Če so ti pogoji izpolnjeni, skoči na etiketo. V nasprotnem primeru pade skozi.

LOOPNE zmanjša ECX in preveri, ali ECX ni nič in ZF NI nastavljen (tj. je nič). Če so ti pogoji izpolnjeni, skoči na oznako. V nasprotnem primeru pade skozi.

Pri x64 register RCX ali njegovi poddeli, kot sta ECX ali CX, hranijo celo število števca. Z navodili LOOP števec običajno odšteva in se zmanjša za 1 za vsak skok (zanko). V naslednjem segmentu kode z zanko se število v registru EAX poveča z 0 na 10 v desetih iteracijah, medtem ko se število v ECX šteje (zmanjša) 10-krat (preberite komentarje):

MOV EAX, 0;

MOV ECX, 10 ; privzeto odšteva 10-krat, enkrat za vsako ponovitev

oznaka:

INC EAX ; prirastek EAX kot telo zanke

Oznaka ZANKA ; zmanjša EAX in če EAX ni nič, ponovno izvede telo zanke iz »label:«

Kodiranje zanke se začne z »label:«. Upoštevajte uporabo dvopičja. Kodiranje zanke se konča z oznako 'LOOP', ki pravi dekrement EAX. Če njegova vsebina ni nič, se vrnite na navodilo za »label:« in znova izvedite katero koli navodilo (vsa navodila telesa), ki pride navzdol do »oznake LOOP«. Upoštevajte, da ima lahko »oznaka« še vedno drugo ime.

6.36 Vhod/izhod x64

Ta del poglavja obravnava pošiljanje podatkov na izhodna (notranja) vrata ali sprejemanje podatkov iz vhodnih (notranjih) vrat. Nabor čipov ima osembitna vrata. Vsaka dva zaporedna 8-bitna vrata se lahko obravnavata kot 16-bitna vrata, katera koli štiri zaporedna vrata pa so lahko 32-bitna vrata. Na ta način lahko procesor prenese 8, 16 ali 32 bitov v ali iz zunanje naprave.

Informacije je mogoče prenašati med procesorjem in notranjimi vrati na dva načina: z uporabo tako imenovanega pomnilniško preslikanega vhoda/izhoda ali z uporabo ločenega vhodno/izhodnega naslovnega prostora. V/I, preslikan v pomnilnik, je podoben temu, kar se zgodi s procesorjem 6502, kjer so naslovi vrat dejansko del celotnega pomnilniškega prostora. V tem primeru gredo podatki pri pošiljanju na določeno lokacijo naslova v vrata in ne v pomnilniško banko. Vrata imajo lahko ločen V/I naslovni prostor. V tem zadnjem primeru imajo vse pomnilniške banke svoje naslove od nič. Obstaja ločen obseg naslovov od 0000H do FFFF16. Uporabljajo jih vrata v naboru čipov. Matična plošča je programirana tako, da ne pride do zamenjave med pomnilniško preslikanim V/I in ločenim V/I naslovnim prostorom.

V/I, preslikan v pomnilnik

S tem se vrata obravnavajo kot pomnilniške lokacije, običajne opcijske kode za uporabo med pomnilnikom in µP pa se uporabljajo za prenos podatkov med µP in vrati. Torej, če želite premakniti bajt iz vrat na naslovu F000H v register µP RAX:EAX:AX:AL, naredite naslednje:

MOV AL, [F000H]

Niz je mogoče premakniti iz pomnilnika v vrata in obratno. primer:

MOVS [F000H], [C000H] ; vir je C000H, cilj pa vrata na F000H.

Ločen V/I naslovni prostor

Pri tem je treba uporabiti posebna navodila za vnos in izhod.

Prenos posameznih elementov

Register procesorja za prenos je RAX. Pravzaprav je RAX:EAX za dvojno besedo, RAX:EAX:AX za besedo in RAX:EAX:AX:AL za bajt. Torej, če želite prenesti bajt iz vrat na FFF0h v RAX:EAX:AX:AL, vnesite naslednje:

V AL, [FFF0H]

Za povratni prenos vnesite naslednje:

IZHOD [FFF0H], AL

Torej, za posamezne predmete so navodila IN in OUT. Naslov vrat je lahko podan tudi v registru RDX:EDX:DX.

Prenos nizov

Niz je mogoče prenesti iz pomnilnika v vrata nabora čipov in obratno. Če želite prenesti niz iz vrat na naslovu FFF0H v pomnilnik, začnite pri C100H, vnesite:

INS [ESI], [DX]

ki ima enak učinek kot:

INS [EDI], [DX]

Programer mora dati dvobajtni naslov vrat FFF0H v register RDX:EDX:Dx in dvobajtni naslov C100H v register RSI:ESI ali RDI:EDI. Za obratni prenos naredite naslednje:

INS [DX], [ESI]

ki ima enak učinek kot:

INS [DX], [EDI]

6.37 The Stack v x64

Tako kot procesor 6502 ima tudi procesor x64 sklad v RAM-u. Sklad za x64 je lahko 2 16 = 65.536 bajtov ali pa je lahko 2 32 = dolžina 4.294.967.296 bajtov. Raste tudi navzdol. Ko je vsebina registra potisnjena v sklad, se število v kazalcu sklada RSP zmanjša za 8. Ne pozabite, da je pomnilniški naslov za x64 širok 64 bitov. Vrednost v kazalcu sklada v µP kaže na naslednjo lokacijo v skladu v RAM-u. Ko je vsebina registra (ali vrednost v enem operandu) prestavljena iz sklada v register, se število v kazalcu sklada RSP poveča za 8. Operacijski sistem določi velikost sklada in kje se začne v RAM-u in raste navzdol. Ne pozabite, da je sklad struktura LIFO (Last-In-First-Out), ki v tem primeru raste navzdol in se krči navzgor.

Če želite potisniti vsebino registra µP RBX v sklad, naredite naslednje:

PRITISNI RBX

Če želite zadnji vnos v skladu vrniti v RBX, naredite naslednje:

POP RBX

6.38 Postopek v x64

Podprogram v x64 se imenuje 'postopek'. Sklad se tu uporablja bolj kot za 6502 µP. Sintaksa za postopek x64 je:

ime_postopka:

telo postopka

…

prav

Preden nadaljujete, upoštevajte, da so kode in oznake za podprogram x64 (splošno navodila za jezik za sestavljanje) neobčutljive na velike in male črke. To pomeni, da je proc_name enako kot PROC_NAME. Tako kot pri 6502 se ime postopka ime (oznaka) začne na začetku nove vrstice v urejevalniku besedil za zbirni jezik. Temu sledi dvopičje in ne presledek in opcijska koda kot pri 6502. Sledi telo podprograma, ki se konča z RET in ne RTS kot pri 6502 µP. Tako kot pri 6502 se vsako navodilo v telesu, vključno z RET, ne začne na začetku svoje vrstice. Upoštevajte, da ima oznaka tukaj lahko več kot 8 znakov. Če želite poklicati ta postopek, nad ali pod vnesenim postopkom, naredite naslednje:

CALL proc_name

Pri 6502 je ime oznake samo tip za klicanje. Vendar pa je tukaj vnesena rezervirana beseda 'CALL' ali 'call', ki ji za presledkom sledi ime postopka (podprograma).

Pri postopkih gre običajno za dva postopka. En postopek kliče drugega. Procedura, ki kliče (ima navodilo za klic), se imenuje 'klicatelj', procedura, ki je klicana, pa se imenuje 'klicanec'. Obstaja konvencija (pravila), ki jih je treba upoštevati.

Pravila klicatelja

Klicatelj se mora pri klicanju podprograma držati naslednjih pravil:

1. Pred klicanjem podprograma mora klicatelj shraniti vsebino določenih registrov, ki so označeni kot shranjeni klicatelj v sklad. Registri, shranjeni pri klicatelju, so R10, R11 in vsi registri, v katere so vneseni parametri (RDI, RSI, RDX, RCX, R8, R9). Če naj se vsebina teh registrov ohrani med klicem podprograma, jih potisnite na sklad, namesto da jih shranite v RAM. To je treba storiti, ker mora klicani uporabiti registre za brisanje prejšnje vsebine.

2. Če je postopek na primer seštevanje dveh števil, sta dve števili parametra, ki ju je treba posredovati v sklad. Če želite parametre posredovati podprogramu, jih vnesite šest v naslednje registre po vrstnem redu: RDI, RSI, RDX, RCX, R8, R9. Če je v podprogramu več kot šest parametrov, preostale potisnite na sklad v obratnem vrstnem redu (tj. prvi parameter zadnji). Ker sklad raste navzdol, je prvi od dodatnih parametrov (pravzaprav sedmi parameter) shranjen na najnižjem naslovu (ta inverzija parametrov je bila v preteklosti uporabljena za omogočanje posredovanja funkcij (podprogramov) s spremenljivim številom parametrov).

3. Za klic podprograma (postopka) uporabite klicno navodilo. To navodilo postavi povratni naslov na vrh parametrov v skladu (najnižji položaj) in veje do kode podprograma.

4. Ko se podprogram vrne (tj. takoj po ukazu klica), mora klicatelj odstraniti vse dodatne parametre (poleg šestih, ki so shranjeni v registrih) iz sklada. S tem se sklad obnovi v stanje, preden je bil klic izveden.

5. Klicatelj lahko pričakuje, da bo našel povratno vrednost (naslov) podprograma v registru RAX.

6. Klicatelj obnovi vsebino registrov, ki jih je shranil klicatelj (R10, R11 in kateri koli v registrih za posredovanje parametrov), tako da jih izloči iz sklada. Klicatelj lahko domneva, da podprogram ni spremenil nobenih drugih registrov.

Zaradi načina, kako je klicna konvencija strukturirana, je običajno tako, da nekateri (ali večina) teh korakov ne bodo spremenili sklada. Na primer, če je parametrov šest ali manj, se v tem koraku nič ne potisne na sklad. Podobno programerji (in prevajalniki) običajno hranijo rezultate, ki jih zanimajo, zunaj registrov, shranjenih pri klicatelju, v korakih 1 in 6, da preprečijo odvečne potiske in poke.

Obstajata še dva načina za posredovanje parametrov v podprogram, vendar ju ta spletni poklicni tečaj ne bo obravnaval. Eden od njih uporablja sam sklad namesto splošnih registrov.

Pravila klicanega

Definicija klicanega podprograma mora upoštevati naslednja pravila:

1. Dodelite lokalne spremenljivke (spremenljivke, ki so razvite znotraj postopka) z uporabo registrov ali ustvarjanjem prostora na skladu. Spomnite se, da kup raste navzdol. Torej, da naredite prostor na vrhu sklada, je treba kazalec sklada zmanjšati. Količina, za katero se kazalec sklada zmanjša, je odvisna od potrebnega števila lokalnih spremenljivk. Na primer, če sta zahtevana lokalni float in lokalni long (skupaj 12 bajtov), je treba kazalec sklada zmanjšati za 12, da naredite prostor za te lokalne spremenljivke. V jeziku na visoki ravni, kot je C, to pomeni deklaracijo spremenljivk brez dodeljevanja (inicializacije) vrednosti.

2. Nato je treba shraniti vrednosti vseh registrov, ki so označeni kot shranjeni za klicatelja (registri splošnega namena, ki jih klicatelj ne shrani), ki jih uporablja funkcija. Če želite shraniti registre, jih potisnite na sklad. Registri, shranjeni pri klicatelju, so RBX, RBP in R12 do R15 (RSP prav tako ohranja klicna konvencija, vendar ga med tem korakom ni treba potisniti v sklad).

Ko so ta tri dejanja izvedena, se lahko nadaljuje dejansko delovanje podprograma. Ko je podprogram pripravljen za vrnitev, se pravila klica nadaljujejo.

3. Ko je podprogram končan, je treba vrnjeno vrednost za podprogram postaviti v RAX, če še ni tam.

4. Podprogram mora obnoviti stare vrednosti vseh registrov, shranjenih pri klicanih (RBX, RBP in R12 do R15), ki so bili spremenjeni. Vsebina registra se obnovi tako, da se izloči iz sklada. Upoštevajte, da je treba registre odpreti v obratnem vrstnem redu, kot so bili potisnjeni.

5. Nato sprostimo lokalne spremenljivke. Najlažji način za to je, da RSP dodate enak znesek, kot ste ga odšteli v 1. koraku.

6. Na koncu se vrnemo k klicalcu z izvedbo ukaza ret. To navodilo poišče in odstrani ustrezen povratni naslov iz sklada.

Primer telesa podprograma klicatelja za klic drugega podprograma, ki je »myFunc«, je naslednji (preberite komentarje):

; Želite poklicati funkcijo 'myFunc', ki potrebuje tri

; celoštevilski parameter. Prvi parameter je v RAX.

; Drugi parameter je konstanta 456. Tretji

; parameter je na pomnilniški lokaciji ”variabl”

potisni rdi; rdi bo param, zato ga shranite

; long retVal = myFunc (x, 456, z);

mov rdi, rax; daj prvi parameter v RDI

mov rsi, 456; postavite drugi parameter v RSI

mov rdx, [spremenljivka]; postavite tretji parameter v RDX

pokliči myFunc ; pokličite funkcijo

pop rdi ; obnovite shranjeno vrednost RDI

; vrnjena vrednost myFunc je zdaj na voljo v RAX

Primer klicane funkcije (myFunc) je (preberite komentarje):

myFunc:

; ∗∗∗ Standardni prolog podprograma ∗∗∗

sub rsp, 8 ; prostor za 64-bitno lokalno spremenljivko (rezultat) z uporabo »pod« kode

potisni rbx; shrani klicanega-shrani registre

potisni rbp; oba bo uporabljal myFunc

; ∗∗∗ Podrutina Telo ∗∗∗

mov rax, rdi; parameter 1 na RAX

mov rbp, rsi; parameter 2 na RBP

mov rbx, rdx; parameter 3 do rb x

mov [rsp + 1 6], rbx; postavite rbx v lokalno spremenljivko

dodaj [rsp + 1 6], rbp; dodajte rbp v lokalno spremenljivko

mov rax, [rsp +16]; mov vsebine lokalne spremenljivke v RAX

; (vrnjena vrednost/končni rezultat)

; ∗∗∗ Standardni epilog podprograma ∗∗∗

pop rbp; obnoviti klicane shranjevalne registre

pop rbx; obratno kot pri pritisku

dodajte rsp, 8; sprosti lokalno spremenljivko(e). 8 pomeni 8 bajtov

ret ; pop top value iz sklada, skoči tja

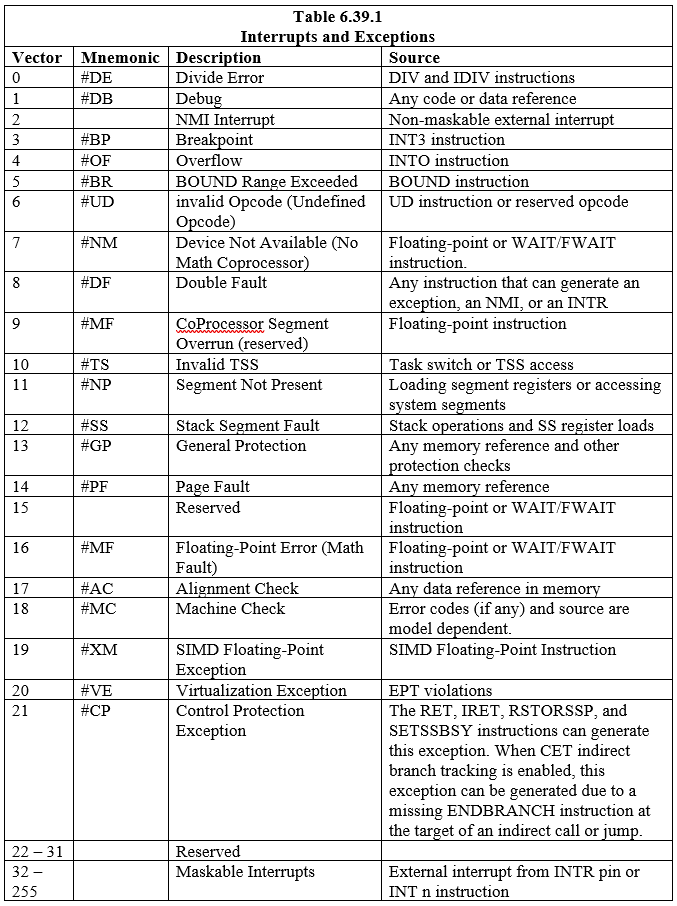

6.39 Prekinitve in izjeme za x64

Procesor ponuja dva mehanizma za prekinitev izvajanja programa, prekinitve in izjeme:

- Prekinitev je asinhroni (lahko se zgodi kadar koli) dogodek, ki ga običajno sproži V/I naprava.

- Izjema je sinhroni dogodek (zgodi se med izvajanjem kode, vnaprej programirano, na podlagi nekega dogodka), ki se ustvari, ko procesor med izvajanjem ukaza zazna enega ali več vnaprej določenih pogojev. Določeni so trije razredi izjem: napake, pasti in prekinitve.

Procesor se na prekinitve in izjeme odziva v bistvu na enak način. Ko je signalizirana prekinitev ali izjema, procesor ustavi izvajanje trenutnega programa ali naloge in preklopi na proceduro obdelovalca, ki je napisana posebej za obravnavo prekinitve ali izjemnega stanja. Procesor dostopa do postopka obravnave prek vnosa v tabeli deskriptorjev prekinitev (IDT). Ko upravljavec zaključi obravnavo prekinitve ali izjeme, se nadzor programa vrne k prekinjenemu programu ali opravilu.

Operacijski sistem, izvršni in/ali gonilniki naprav običajno obravnavajo prekinitve in izjeme neodvisno od aplikacijskih programov ali nalog. Aplikacijski programi pa lahko dostopajo do upravljavcev prekinitev in izjem, ki so vključeni v operacijski sistem, ali pa ga izvajajo prek klicev v zbirnem jeziku.

Definiranih je osemnajst (18) preddefiniranih prekinitev in izjem, ki so povezane z vnosi v IDT. Prav tako je mogoče narediti dvesto štiriindvajset (224) uporabniško definiranih prekinitev in jih povezati s tabelo. Vsaka prekinitev in izjema v IDT je identificirana s številko, ki se imenuje 'vektor'. Tabela 6.39.1 navaja prekinitve in izjeme z vnosi v IDT in njihove ustrezne vektorje. Vektorji od 0 do 8, od 10 do 14 in od 16 do 19 so vnaprej določene prekinitve in izjeme. Vektorji od 32 do 255 so za programsko definirane prekinitve (uporabnik), ki so bodisi za prekinitve programske opreme bodisi za maskirne prekinitve strojne opreme.

Ko procesor zazna prekinitev ali izjemo, naredi eno od naslednjih stvari:

- Izvedite implicitni klic procedure obdelovalca

- Izvedite implicitni klic naloge upravljalnika

6.4 Osnove arhitekture 64-bitnega računalnika ARM

Arhitekture ARM definirajo družino procesorjev RISC, ki so primerni za uporabo v najrazličnejših aplikacijah. ARM je arhitektura nalaganja/shranjevanja, ki zahteva, da se podatki naložijo iz pomnilnika v register, preden se lahko z njimi izvede kakršna koli obdelava, kot je operacija ALU (Aritmetično logična enota). Naknadno navodilo shrani rezultat nazaj v pomnilnik. Čeprav se to morda zdi kot korak nazaj od arhitektur x86 in x64, ki delujeta neposredno na operande v pomnilniku v enem samem ukazu (seveda z uporabo procesorskih registrov), pristop nalaganja/shranjevanja v praksi dovoljuje več zaporednih operacij izvesti z visoko hitrostjo na operandu, ko je naložen v enega od številnih procesorskih registrov. Procesorji ARM imajo možnost little endianness ali big-endianness. Privzeta nastavitev ARM 64 je little-endian, kar je konfiguracija, ki jo običajno uporabljajo operacijski sistemi. 64-bitna arhitektura ARM je sodobna in naj bi nadomestila 32-bitno arhitekturo ARM.

Opomba : Vsako navodilo za 64-bitni ARM µP je dolgo 4 bajte (32 bitov).

6.41 64-bitni nabor registrov ARM

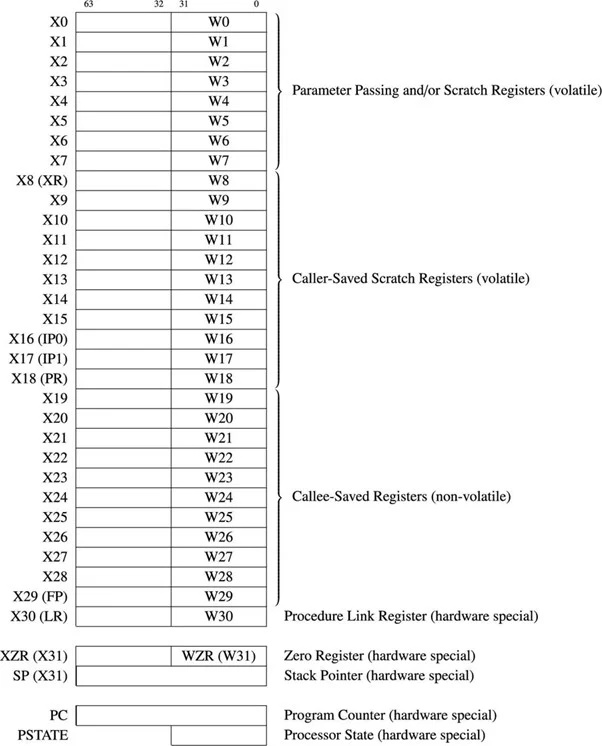

Obstaja 31 splošnih 64-bitnih registrov za 64-bitni ARM µP. Naslednji diagram prikazuje registre splošnega namena in nekaj pomembnih registrov:

Slika 4.11.1 64-bitni splošni namen in nekateri pomembni registri

Splošni registri se imenujejo X0 do X30. Prvi 32-bitni del za vsak register se imenuje W0 do W30. Kadar razlika med 32 in 64 biti ni poudarjena, se uporabi predpona »R«. Na primer, R14 se nanaša na W14 ali X14.

6502 µP ima 16-bitni programski števec in lahko obravnava 2 16 pomnilniške lokacije bajtov. 64-bitni ARM µP ima 64-bitni programski števec in lahko naslovi do 2 64 = 1,844674407 x 1019 (dejansko 18,446,744,073,709,551,616) pomnilniških lokacij bajtov. Programski števec vsebuje naslov naslednjega ukaza, ki ga je treba izvesti. Dolžina ukaza ARM64 ali AArch64 je običajno štiri bajte. Procesor samodejno poveča ta register za štiri po vsakem ukazu, pridobljenem iz pomnilnika.

Register kazalca sklada ali SP ni med 31 registri splošnega namena. Kazalec sklada katere koli arhitekture kaže na zadnji vnos sklada v pomnilniku. Pri ARM-64 sklad raste navzdol.

6502 µP ima 8-bitni register statusa procesorja. Ekvivalent v ARM64 se imenuje register PSTATE. Ta register shranjuje zastavice, ki se uporabljajo za rezultate operacij in za krmiljenje procesorja (µP). Širok je 32 bitov. Naslednja tabela podaja imena, indekse in pomene pogosto uporabljenih bitov v registru PSTATE:

| Tabela 6.41.1 Najpogosteje uporabljene zastavice PSTATE (biti) |

||

|---|---|---|

| Simbol | bit | Namen |

| M | 0-3 | Način: trenutna raven privilegijev izvajanja (USR, SVC itd.). |

| T | 4 | Thumb: Nastavi se, če je aktiven nabor ukazov T32 (Thumb). Če je prazno, je nabor navodil ARM aktiven. Uporabniška koda lahko nastavi in počisti ta bit. |

| IN | 9 | Endianness: Nastavitev tega bita omogoči način big-endian. Če je jasno, je način little-endian aktiven. Privzeto je način little-endian. |

| Q | 27 | Zastavica kumulativne nasičenosti: Nastavi se, če na neki točki v nizu operacij pride do preliva ali nasičenosti |

| IN | 28 | Zastavica prelivanja: Nastavljena je, če je operacija povzročila podpisano prelivanje. |

| C | 29 | Zastavica za prenos: označuje, ali je seštevanje povzročilo prenos ali odštevanje izposojo. |

| Z | 30 | Zastavica nič: Nastavi se, če je rezultat operacije nič. |

| N | 31 | Negativna zastavica: Nastavi se, če je rezultat operacije negativen. |

ARM-64 µP ima veliko drugih registrov.

SIMD

SIMD je kratica za Single Instruction, Multiple Data. To pomeni, da lahko en ukaz zbirnega jezika deluje na več podatkih hkrati v enem mikroprocesorju. Obstaja dvaintrideset 128-bitnih širokih registrov za uporabo s SIMD in operacijami s plavajočo vejico.

6.42 Preslikava pomnilnika

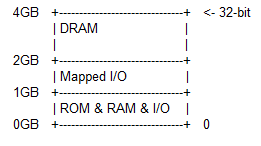

RAM in DRAM sta pomnilnika z naključnim dostopom. DRAM deluje počasneje kot RAM. DRAM je cenejši od RAM-a. Če je v pomnilniku več kot 32 gigabajtov (GB) neprekinjenega DRAM-a, bo več težav pri upravljanju pomnilnika: 32 GB = 32 x 1024 x 1024 x 1024 bajtov. Za celoten pomnilniški prostor, ki je veliko večji od 32 GB, mora biti DRAM nad 32 GB premešan z RAM-i za boljše upravljanje pomnilnika. Da bi razumeli zemljevid pomnilnika ARM-64, morate najprej razumeti zemljevid pomnilnika 4 GB za 32-bitno centralno procesorsko enoto (CPE) ARM. CPU pomeni µP. Za 32-bitni računalnik je največji pomnilniški naslovljivi prostor 2 32 = 4 x 2 10 x 2 10 x 2 10 = 4 x 1024 x 1024 x 1024 = 4.294.967.296 = 4 GB.

32-bitni zemljevid pomnilnika ARM

Zemljevid pomnilnika za 32-bitni ARM je:

Za 32-bitni računalnik je največja velikost celotnega pomnilnika 4 GB. Od naslova 0 GB do naslova 1 GB so lokacije operacijskega sistema ROM, RAM in V/I. Celotna zamisel o ROM OS, RAM in I/O naslovih je podobna situaciji Commodore-64 z možnim CPU 6502. OS ROM za Commodore-64 je na vrhu pomnilniškega prostora. Tukajšnji ROM OS je veliko večji kot pri Commodore-64 in je na začetku celotnega pomnilniškega naslovnega prostora. V primerjavi z drugimi sodobnimi računalniki je tukaj ROM OS popoln, v smislu, da je primerljiv s količino OS na njihovih trdih diskih. Obstajata dva glavna razloga za uporabo OS v integriranih vezjih ROM: 1) CPE ARM se večinoma uporabljajo v majhnih napravah, kot so pametni telefoni. Mnogi trdi diski so večji od pametnih telefonov in drugih majhnih naprav, 2) zaradi varnosti. Ko je OS v pomnilniku samo za branje, ga hekerji ne morejo poškodovati (prepisati delov). Odseki RAM in vhodno/izhodni odseki so prav tako zelo veliki v primerjavi s tistimi pri Commodore-64.

Ko je napajanje vklopljeno z 32-bitnim OS ROM, se mora OS zagnati (zagnati z) naslova 0x00000000 ali naslova 0xFFFF0000, če je omogočen HiVECs. Torej, ko je napajanje vklopljeno po fazi ponastavitve, strojna oprema CPE naloži 0x00000000 ali 0xFFFF0000 v programski števec. Predpona »0x« pomeni šestnajstiško. Zagonski naslov 64-bitnih procesorjev ARMv8 je definirana izvedba. Vendar pa avtor svetuje računalniškemu inženirju, naj začne pri 0x00000000 ali 0xFFFF0000 zaradi združljivosti za nazaj.

Od 1 GB do 2 GB je preslikan vhod/izhod. Obstaja razlika med preslikanimi V/I in samo V/I, ki jih najdemo med 0 GB in 1 GB. Pri V/I je naslov za vsaka vrata fiksen kot pri Commodore-64. Pri preslikanem V/I naslov za vsaka vrata ni nujno enak za vsako operacijo računalnika (dinamičen).

Od 2 GB do 4 GB je DRAM. To je pričakovani (ali običajni) RAM. DRAM pomeni dinamični RAM, ne pomeni spreminjanja naslova med delovanjem računalnika, ampak v smislu, da je treba vrednost vsake celice v fizičnem RAM-u osvežiti ob vsakem utripu.

Opomba :

- Od 0x0000,0000 do 0x0000 je FFFF OS ROM.

- Od 0x0001,0000 do 0x3FFF,FFFF je lahko več ROM-a, nato RAM-a in nato nekaj V/I.

- Od 0x4000,0000 do 0x7FFF,FFFF je dovoljen dodatni V/I in/ali preslikan V/I.

- Od 0x8000,0000 do 0xFFFF je FFFF pričakovan DRAM.

To pomeni, da pričakovanemu DRAM-u v praksi ni treba začeti pri meji 2 GB pomnilnika. Zakaj bi moral programer spoštovati idealne meje, če ni dovolj fizičnih bank RAM-a, ki so nameščeni na matični plošči? To je zato, ker stranka nima dovolj denarja za vse banke RAM.

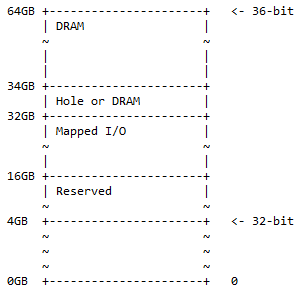

36-bitni zemljevid pomnilnika ARM

Pri 64-bitnem računalniku ARM se vseh 32 bitov uporablja za naslavljanje celotnega pomnilnika. Za 64-bitni računalnik ARM se lahko prvih 36 bitov uporabi za naslov celotnega pomnilnika, ki je v tem primeru 2 36 = 68.719.476.736 = 64 GB. To je že veliko spomina. Današnji navadni računalniki ne potrebujejo te količine pomnilnika. To še ni doseglo največjega obsega pomnilnika, do katerega lahko dostopa 64 bitov. Pomnilniška karta za 36-bitne procesorje ARM je:

Od naslova 0 GB do naslova 4 GB je 32-bitni zemljevid pomnilnika. »Rezervirano« pomeni, da se ne uporablja in se hrani za prihodnjo uporabo. Za ta prostor ni nujno, da so na matični plošči nameščene fizične pomnilniške banke. Tukaj imata DRAM in preslikani V/I enak pomen kot za 32-bitni pomnilniški zemljevid.

V praksi se lahko pojavi naslednja situacija:

- 0x1 0000 0000 – 0x3 FFFF FFFF; rezerviran. 12 GB naslovnega prostora je rezerviranega za prihodnjo uporabo.

- 0x4 0000 0000 – 0x7 FFFF FFFF; preslikan V/I. Za dinamično preslikan V/I je na voljo 16 GB naslovnega prostora.

- 0x8 0000 0000 – 0x8 7FFF FFFF FFFF; Luknja ali DRAM. 2 GB naslovnega prostora lahko vsebuje kar koli od naslednjega:

- Luknja za omogočanje particioniranja naprave DRAM (kot je opisano v naslednji razpravi).

- DRAM.

- 0x8 8000 0000 – 0xF FFFF FFFF; DRAM. 30 GB naslovnega prostora za DRAM.

Ta pomnilniški zemljevid je nadnabor 32-bitnega naslovnega zemljevida, pri čemer je dodatni prostor razdeljen kot 50 % DRAM (1/2) z izbirno luknjo v njem in 25 % preslikanega V/I prostora in rezerviranega prostora (1/4 ). Preostalih 25 % (1/4) je za 32-bitni pomnilniški zemljevid ½ + ¼ + ¼ = 1.

Opomba : Od 32 bitov do 360 bitov je dodatek 4 bitov k najpomembnejši strani 36 bitov.

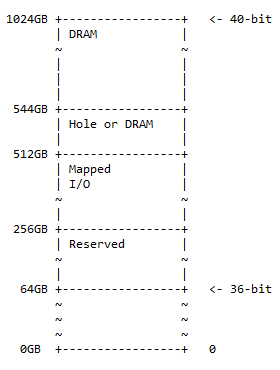

40-bitni pomnilniški zemljevid

40-bitni zemljevid naslovov je nadmnožica 36-bitnega zemljevida naslovov in sledi istemu vzorcu 50 % DRAM-a z neobvezno luknjo v njem, 25 % preslikanega V/I prostora in rezerviranega prostora ter preostalih 25 % prostor za prejšnji pomnilniški zemljevid (36-bitni). Diagram za pomnilniški zemljevid je:

Velikost luknje je 544 – 512 = 32 GB. V praksi se lahko pojavi naslednja situacija:

- 0x10 0000 0000 – 0x3F FFFF FFFF; rezerviran. 192 GB naslovnega prostora je rezerviranega za prihodnjo uporabo.

- 0x40 0000 0000 – 0x7F FFFF FFFF; preslikano. V/I. Za dinamično preslikan V/I je na voljo 256 GB naslovnega prostora.

- 0x80 0000 0000 – 0x87 FFFF FFFF; luknjo ali DRAM. 32 GB naslovnega prostora lahko vsebuje kar koli od naslednjega:

- Luknja za omogočanje particioniranja naprave DRAM (kot je opisano v naslednji razpravi)

- DRAM

- 0x88 0000 0000 – 0xFF FFFF FFFF; DRAM. 480 GB naslovnega prostora za DRAM.

Opomba : Od 36 bitov do 40 bitov je dodatek 4 bitov k najpomembnejši strani 36 bitov.

DRAM luknja

V zemljevidu pomnilnika, ki presega 32 bitov, je luknja DRAM ali nadaljevanje DRAM-a z vrha. Če gre za luknjo, jo je treba razumeti na naslednji način: luknja DRAM omogoča razdelitev velike naprave DRAM na več obsegov naslovov. Izbirna luknja DRAM je predlagana na začetku višje naslovne meje DRAM. To omogoča poenostavljeno shemo dekodiranja pri particioniranju naprave DRAM z veliko zmogljivostjo po spodnjem fizično naslovljenem območju.

Na primer, del DRAM-a s 64 GB je razdeljen na tri regije z odmiki naslovov, ki se izvajajo s preprostim odštevanjem bitov naslova višjega reda, kot sledi:

| Tabela 6.42.1 Primer particioniranja 64 GB DRAM z luknjami |

|||

|---|---|---|---|

| Fizični naslovi v SoC | Odmik | Notranji naslov DRAM | |

| 2 GB (32-bitni zemljevid) | 0x00 8000 0000 – 0x00 FFFF FFFF | -0x00 8000 0000 | 0x00 0000 0000 – 0x00 7FFF FFFF |

| 30 GB (36-bitni zemljevid) | 0x08 8000 0000 – 0x0F FFFF FFFF | -0x08 0000 0000 | 0x00 8000 0000 – 0x07 FFFF FFFF |

| 32 GB (40-bitni zemljevid) | 0x88 0000 0000 – 0x8F FFFF FFFF | -0x80 0000 0000 | 0x08 0000 0000 – 0x0F FFFF FFFF |

Predlagani 44-bitni in 48-bitni naslovljeni pomnilniški zemljevidi za procesorje ARM

Predpostavimo, da ima osebni računalnik 1024 GB (= 1 TB) pomnilnika; to je preveč spomina. In tako so 44-bitni in 48-bitni naslovljeni pomnilniški zemljevidi za procesorje ARM za 16 TB oziroma 256 TB le predlogi za prihodnje računalniške potrebe. Pravzaprav ti predlogi za procesorje ARM sledijo isti delitvi pomnilnika po razmerju kot prejšnji pomnilniški zemljevidi. To je: 50 % DRAM-a z neobvezno luknjo v njem, 25 % preslikanega V/I prostora in rezerviranega prostora ter preostalih 25 % prostora za prejšnji pomnilniški zemljevid.

52-bitni, 56-bitni, 60-bitni in 64-bitni naslovljeni pomnilniški zemljevidi bodo še vedno predlagani za 64-bitni ARM za daljno prihodnost. Če se bo takratnim znanstvenikom delitev celotnega pomnilniškega prostora v razmerju 50 : 25 : 25 še vedno zdela koristna, bodo razmerje ohranili.

Opomba : SoC je kratica za System-on-Chip, ki se nanaša na vezja v čipu µP, ki jih sicer tam ne bi bilo.

SRAM ali statični pomnilnik z naključnim dostopom je hitrejši od bolj tradicionalnega DRAM-a, vendar zahteva več silikonske površine. SRAM ne potrebuje osveževanja. Bralec si lahko predstavlja RAM kot SRAM.

6.43 Načini naslavljanja zbirnega jezika za ARM 64

ARM je arhitektura nalaganja/shranjevanja, ki zahteva, da se podatki naložijo iz pomnilnika v register procesorja, preden se lahko z njimi izvede kakršna koli obdelava, kot je aritmetična logična operacija. Naknadno navodilo shrani rezultat nazaj v pomnilnik. Čeprav se to morda zdi kot korak nazaj v primerjavi z arhitekturo x86 in njenimi kasnejšimi arhitekturami x64, ki delujejo neposredno na operande v pomnilniku v enem samem ukazu, v praksi pristop nalaganja/shranjevanja dovoljuje izvajanje več zaporednih operacij pri visoki hitrosti na operand, ko je naložen v enega od številnih procesorskih registrov.

Format zbirnega jezika ARM ima podobnosti in razlike s serijo x64 (x86).

- Odmik : V osnovni register je mogoče dodati konstanto s predznakom. Odmik je vnesen kot del navodil. Na primer: ldr x0, [rx, #10] naloži r0 z besedo na naslovu r1+10.

- Registrirajte se : Nepredznačeni prirastek, ki je shranjen v registru, je mogoče dodati ali odšteti od vrednosti v osnovnem registru. Na primer: ldr r0, [x1, x2] naloži r0 z besedo na naslovu x1+x2. Kateri koli od registrov je mogoče obravnavati kot osnovni register.

- Skalirani register : Povečanje v registru se premakne levo ali desno za določeno število bitnih položajev, preden se doda ali odšteje od vrednosti osnovnega registra. Na primer: ldr x0, [x1, x2, lsl #3] naloži r0 z besedo na naslov r1+(r2×8). Premik je lahko logični levi ali desni premik (lsl ali lsr), ki vstavi ničelne bite na izpraznjene bitne položaje, ali aritmetični desni premik (asr), ki ponovi predznakovni bit na izpraznjenih položajih.

Ko sta vključena dva operanda, je cilj pred (na levi) izvorom (pri tem je nekaj izjem). Operacijske kode za zbirni jezik ARM ne razlikujejo med velikimi in malimi črkami.

Takojšen način naslavljanja ARM64

primer:

mov r0, #0xFF000000; Naložite 32-bitno vrednost FF000000h v r0

Decimalna vrednost je brez 0x, vendar je še vedno pred njo #.

Registrirajte se neposredno

primer:

mov x0, x1; Kopirajte x1 v x0

Registracija posredno

primer:

str x0, [x3] ; Shranite x0 na naslov v x3

Registrirajte posredno z odmikom

Primeri:

ldr x0, [x1, #32] ; Naloži r0 z vrednostjo na naslov [r1+32]; r1 je osnovni register

str x0, [x1, #4] ; Shranite r0 na naslov [r1+4]; r1 je osnovni register; števila so osnova 10

Registriraj posredno z odmikom (predhodno povečano)

Primeri:

ldr x0, [x1, #32]! ; Naloži r0 z [r1+32] in posodobi r1 na (r1+32)

str x0, [x1, #4]! ; Shranite r0 v [r1+4] in posodobite r1 v (r1+4)

Upoštevajte uporabo '!' simbol.

Registriraj posredno z odmikom (naknadno povečano)

Primeri:

ldr x0, [x1], #32; Naloži [x1] na x0, nato posodobi x1 na (x1+32)

str x0, [x1], #4; Shranite x0 v [x1], nato posodobite x1 v (x1+4)

Posredni dvojni register

Naslov operanda je vsota osnovnega registra in registra povečanja. Imena registrov so obdana z oglatimi oklepaji.

Primeri:

ldr x0, [x1, x2] ; Naloži x0 z [x1+x2]

str x0, [rx, x2] ; Shrani x0 v [x1+x2]

Način relativnega naslavljanja

V načinu relativnega naslavljanja je učinkovito navodilo naslednje navodilo v programskem števcu in indeks. Indeks je lahko pozitiven ali negativen.

primer:

ldr x0, [pc, #24]

To pomeni naložitveni register X0 z besedo, na katero kaže vsebina računalnika, plus 24.

6.44 Nekaj pogosto uporabljenih navodil za ARM 64

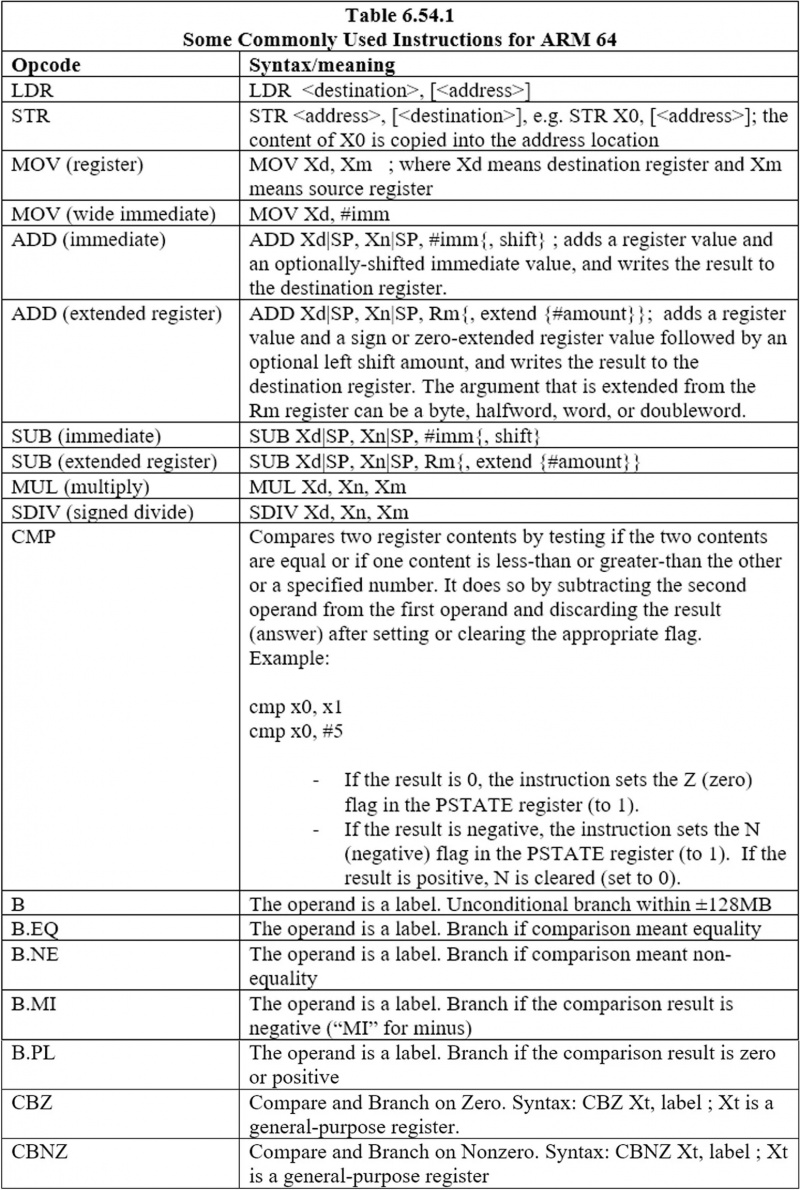

Tukaj so pogosto uporabljena navodila:

6.45 Looping

Ilustracija

Naslednja koda dodaja vrednost v registru X10 vrednosti v X9, dokler vrednost v X8 ni enaka nič. Predpostavimo, da so vse vrednosti cela števila. Vrednost v X8 se v vsaki ponovitvi odšteje za 1:

zanka:

CBZ X8, preskoči

DODAJ X9, X9, X10 ; prvi X9 je cilj, drugi X9 pa vir

SUB X8, X8, #1 ; prvi X8 je cilj, drugi X8 pa vir

B zanka

preskoči:

Tako kot pri 6502 µP in X64 µP se oznaka pri ARM 64 µP začne na začetku vrstice. Preostala navodila se začnejo na nekaj mestih po začetku vrstice. Pri x64 in ARM 64 oznaki sledita dvopičje in nova vrstica. Pri 6502 pa oznaki sledi navodilo za presledkom. V prejšnji kodi prvo navodilo, ki je »CBZ X8, preskoči«, pomeni, da če je vrednost v X8 nič, nadaljujte pri oznaki »preskoči:«, preskočite vmesna navodila in nadaljujte s preostalimi navodili spodaj. 'preskoči:'. »B zanka« je brezpogojni skok na oznako »zanka«. Namesto 'zanke' lahko uporabite katero koli drugo ime oznake.

Torej, tako kot pri 6502 µP, uporabite navodila za razvejanje, da imate zanko z ARM 64.

6.46 ARM 64 Vhod/Izhod

Vse periferne naprave ARM (notranja vrata) so preslikane v pomnilnik. To pomeni, da je programski vmesnik niz pomnilniško naslovljenih registrov (notranja vrata). Naslov takega registra je odmik od določenega osnovnega naslova pomnilnika. To je podobno temu, kako 6502 izvaja vhod/izhod. ARM nima možnosti za ločen V/I naslovni prostor.

6.47 Sklad ARM 64

ARM 64 ima sklad v pomnilniku (RAM) na podoben način kot 6502 in x64. Vendar pa pri ARM64 ni potisne ali pop kode. Tudi sklad v ARM 64 raste navzdol. Naslov v kazalcu sklada kaže takoj za zadnjim bajtom zadnje vrednosti, ki je postavljena v sklad.

Razlog, zakaj za ARM64 ni generične pop ali push opcode, je, da ARM 64 upravlja svoj sklad v skupinah zaporednih 16 bajtov. Vendar pa vrednosti obstajajo v skupinah bajtov po enem bajtu, dveh bajtih, štirih bajtih in 8 bajtih. Tako je eno vrednost mogoče postaviti v sklad, preostala mesta (lokacije bajtov), ki nadomestijo 16 bajtov, pa so dopolnjena z navideznimi bajti. Pomanjkljivost tega je zapravljanje pomnilnika. Boljša rešitev je, da 16-bajtno lokacijo zapolnite z manjšimi vrednostmi in da programerju napiše kodo, ki sledi, od kod prihajajo vrednosti na 16-bajtni lokaciji (registri). Ta dodatna koda je potrebna tudi za vračanje vrednosti. Alternativa temu je, da izpolnite dva 8-bajtna registra splošnega namena z različnimi vrednostmi in nato pošljete vsebino obeh 8-bajtnih registrov v sklad. Tukaj je še vedno potrebna dodatna koda za sledenje specifičnim majhnim vrednostim, ki gredo v sklad in zapustijo sklad.

Naslednja koda shrani štiri 4-bajtne podatke v sklad:

str w0, [sp, #-4]!

str w1, [sp, #-8]!

str w2, [sp, #-12]!

str w3, [sp, #-16]!

Prvi štirje bajti (w) registrov – x0, x1, x2 in x3 – so poslani na 16-zaporedna bajtna mesta v skladu. Upoštevajte uporabo »str« in ne »push«. Bodite pozorni na simbol klicaja na koncu vsakega navodila. Ker pomnilniški sklad raste navzdol, se prva štiribajtna vrednost začne na položaju, ki je minus štiri bajte pod prejšnjim položajem kazalca sklada. Preostale štiribajtne vrednosti sledijo navzdol. Naslednji segment kode bo izvedel pravilen (in vrstni red) ekvivalent izločanja štirih bajtov:

ldr w3, [sp], #0

ldr w2, [sp], #4

ldr w1, [sp], #8

ldr w0, [sp], #12

Upoštevajte uporabo operacijske kode ldr namesto pop. Upoštevajte tudi, da simbol klicaja tukaj ni uporabljen.

Vse bajte v X0 (8 bajtov) in X1 (8 bajtov) je mogoče poslati na 16-bajtno lokacijo v skladu, kot sledi:

stp x0, x1, [sp, #-16]! ; 8 + 8 = 16

V tem primeru registra x2 (w2) in x3 (w3) nista potrebna. Vsi želeni bajti so v registrih X0 in X2. Upoštevajte opcijsko kodo stp za shranjevanje parov vsebin registra v RAM. Upoštevajte tudi simbol klicaja. Ekvivalent popa je:

ldp x0, x1, [sp], #0

Za to navodilo ni klicaja. Upoštevajte operacijsko kodo LDP namesto LDR za nalaganje dveh zaporednih podatkovnih lokacij iz pomnilnika v dva registra µP. Ne pozabite tudi, da je kopiranje iz pomnilnika v register µP nalaganje, ki ga ne smemo zamenjevati z nalaganjem datoteke z diska v RAM, kopiranje iz registra µP v RAM pa je shranjevanje.

6.48 Podprogram

Podprogram je blok kode, ki izvede nalogo, neobvezno na podlagi nekaterih argumentov in neobvezno vrne rezultat. Po dogovoru se registri R0 do R3 (štirje registri) uporabljajo za posredovanje argumentov (parametrov) podprogramu, R0 pa se uporablja za posredovanje rezultata nazaj klicatelju. Podprogram, ki potrebuje več kot 4 vnose, uporablja sklad za dodatne vnose. Za klic podprograma uporabite povezavo ali navodilo za pogojno razvejanje. Sintaksa za navodila za povezavo je:

Oznaka BL

Kjer je BL opcode, oznaka pa predstavlja začetek (naslov) podprograma. Ta veja je brezpogojna, naprej ali nazaj znotraj 128 MB. Sintaksa za ukaz pogojnega razvejanja je:

B.cond oznaka

Kjer je cond pogoj, npr. eq (enako) ali ne (ni enako). Naslednji program ima podprogram doadd, ki sešteje vrednosti dveh argumentov in vrne rezultat v R0:

OBMOČJE podizhod, KODA, SAMO ZA BRANJE ; Poimenujte ta blok kode

VSTOP ; Označite prvo navodilo za izvedbo

zagon MOV r0, #10 ; Nastavite parametre

MOV r1, #3

BL dodati ; Pokliči podprogram

ustavi MOV r0, #0x18; angel_SWIreason_ReportException

LDR r1, =0x20026; ADP_Stopped_ApplicationExit

SVC #0x123456 ; ARM polgostovanje (prej SWI)

doadd ADD r0, r0, r1 ; Koda podprograma

BX lr ; Vrnitev iz podprograma

;

KONEC ; Označite konec datoteke

Števili, ki jih je treba dodati, sta decimalno 10 in decimalno 3. Prvi dve vrstici v tem bloku kode (programu) bosta pojasnjeni kasneje. Naslednje tri vrstice pošljejo 10 v register R0 in 3 v register R1 ter pokličejo podprogram doadd. 'Doadd' je oznaka, ki vsebuje naslov začetka podprograma.

Podprogram je sestavljen iz samo dveh vrstic. Prva vrstica doda vsebino 3 R vsebini 10 R0, kar omogoča rezultat 13 v R0. Druga vrstica z operacijsko kodo BX in operandom LR se vrne iz podprograma v kodo klicatelja.

PRAV

Operacijska koda RET v ARM 64 še vedno obravnava podprogram, vendar deluje drugače kot RTS v 6502 ali RET na x64 ali kombinacija »BX LR« v ARM 64. V ARM 64 je sintaksa za RET:

RAVNOST {Xn}

To navodilo omogoča programu, da nadaljuje s podprogramom, ki ni podprogram klicatelja, ali samo nadaljuje z drugim navodilom in njegovim naslednjim segmentom kode. Xn je register splošnega namena, ki vsebuje naslov, na katerega naj se program nadaljuje. To navodilo se brezpogojno razveja. Privzeta je vsebina X30, če Xn ni podan.

Standardni klic postopka

Če programer želi, da njegova koda deluje s kodo, ki jo je napisal nekdo drug, ali s kodo, ki jo je ustvaril prevajalnik, se mora programer z osebo ali piscem prevajalnika dogovoriti o pravilih za uporabo registra. Za arhitekturo ARM se ta pravila imenujejo Procedure Call Standard ali PCS. To so dogovori med dvema ali tremi stranmi. PCS določa naslednje:

- Kateri registri µP se uporabljajo za posredovanje argumentov v funkcijo (podprogram)

- Kateri registri µP se uporabljajo za vrnitev rezultata funkciji, ki kliče in je znana kot klicatelj

- Kateri µP registrira klicano funkcijo, ki je znana kot klicanec, lahko pokvari

- Katere µP registre klicani ne more pokvariti

6.49 Prekinitve

Za procesor ARM sta na voljo dve vrsti vezij za krmiljenje prekinitev:

- Standardni krmilnik prekinitev: Upravljalnik prekinitev določi, katera naprava zahteva servisiranje, tako da prebere register bitne slike naprave v krmilniku prekinitev.

- Vektorski krmilnik prekinitev (VIC): prednostno razvrsti prekinitve in poenostavi določitev, katera naprava je povzročila prekinitev. Po povezovanju prioritete in naslova obdelovalca z vsako prekinitvijo, VIC uveljavlja prekinitveni signal procesorju le, če je prednost nove prekinitve višja od trenutno izvajajočega se obdelovalca prekinitev.

Opomba : Izjema se nanaša na napako. Podrobnosti za krmilnik vektorskih prekinitev za 32-bitni računalnik ARM so naslednje (64-bitni je podoben):

| Tabela 6.49.1 Vektorska izjema/prekinitev ARM za 32-bitni računalnik |

|||

|---|---|---|---|

| Izjema/prekinitev | Kratka roka | Naslov | Visoki naslov |

| Ponastaviti | PONASTAVITI | 0x00000000 | 0xffff0000 |

| Nedefinirano navodilo | UNDEF | 0x00000004 | 0xffff0004 |

| Programska prekinitev | SWI | 0x00000008 | 0xffff0008 |

| Prekinitev vnaprejšnjega prenosa | pabt | 0x0000000C | 0xffff000C |

| Datum splava | DABT | 0x00000010 | 0xffff0010 |

| Rezervirano | – | 0x00000014 | 0xffff0014 |

| Zahteva za prekinitev | IRQ | 0x00000018 | 0xffff0018 |

| Zahteva za hitro prekinitev | FIQ | 0x0000001C | 0xffff001C |

To je videti kot ureditev za arhitekturo 6502, kjer NMI , BR , in IRQ ima lahko kazalce na ničelni strani, ustrezne rutine pa so visoko v pomnilniku (ROM OS). Kratki opisi vrstic prejšnje tabele so naslednji:

PONASTAVITI

To se zgodi, ko se procesor vklopi. Inicializira sistem in nastavi sklade za različne načine procesorja. Je najvišja prednostna izjema. Po vstopu v obravnavo ponastavitve je CPSR v načinu SVC in bit IRQ in FIQ sta nastavljena na 1, kar prikrije vse prekinitve.

DATUM PREKINITVE

Druga najvišja prioriteta. To se zgodi, ko poskušamo brati/pisati na neveljaven naslov ali dostopati do napačnega dovoljenja za dostop. Po vstopu v Data Abort Handler bodo IRQ-ji onemogočeni (I-bit set 1) in FIQ bo omogočen. IRQ-ji so maskirani, FIQ-ji pa ostanejo nezamaskirani.

FIQ

Prekinitve z najvišjo prioriteto, IRQ in FIQ, so onemogočene, dokler se ne obravnava FIQ.

IRQ

Prekinitev z visoko prioriteto, upravljalnik IRQ, se vnese le, če ni trenutnega FIQ in prekinitve podatkov.

Prekinitev vnaprejšnjega pridobivanja

To je podobno prekinitvi podatkov, vendar se zgodi ob napaki pridobivanja naslova. Ob vstopu v upravljalnik so IRQ-ji onemogočeni, vendar FIQ-ji ostanejo omogočeni in se lahko zgodijo med prekinitvijo vnaprejšnjega pridobivanja.

SWI

Do izjeme programske prekinitve (SWI) pride, ko se izvede navodilo SWI in nobena od drugih izjem z višjo prioriteto ni označena.

Nedefinirano navodilo

Do izjeme Nedefinirano navodilo pride, ko navodilo, ki ni v nizu navodil ARM ali Thumb, doseže stopnjo izvajanja cevovoda in nobena od drugih izjem ni bila označena. To je enaka prioriteta kot SWI, saj se lahko zgodi ena naenkrat. To pomeni, da navodilo, ki se izvaja, ne more biti istočasno navodilo SWI in nedefinirano navodilo.

Obravnava izjem ARM

Ko pride do izjeme, se zgodijo naslednji dogodki:

- Shranite CPSR v SPSR izjemnega načina.

- PC je shranjen v LR izjemnega načina.

- Register povezav je nastavljen na določen naslov glede na trenutna navodila. Na primer: za ISR je LR = zadnje izvedeno navodilo + 8.

- Posodobite CPSR glede izjeme.

- Nastavite osebni računalnik na naslov obdelovalca izjem.

6.5 Navodila in podatki

Podatki se nanašajo na spremenljivke (oznake z njihovimi vrednostmi) ter nize in druge strukture, ki so podobne nizu. Niz je kot niz znakov. Niz celih števil je viden v enem od prejšnjih poglavij. Navodila se nanašajo na operacijske kode in njihove operande. Program se lahko napiše z operacijskimi kodami in podatki, pomešanimi v enem nadaljevanem delu pomnilnika. Ta pristop ima slabosti, vendar ni priporočljiv.

Program je treba najprej napisati z navodili, ki jim sledijo podatki (množina podatka je podatek). Ločitev med navodili in podatki je lahko le nekaj bajtov. Pri programu so tako navodila kot podatki lahko v enem ali dveh ločenih razdelkih v pomnilniku.

6.6 Harvardska arhitektura

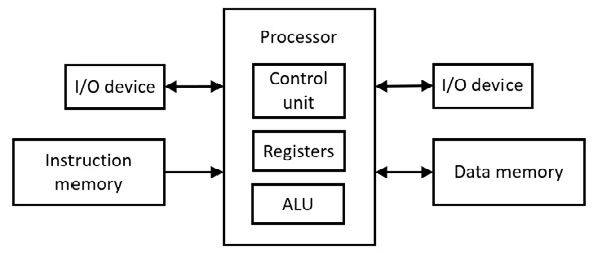

Eden prvih računalnikov se imenuje Harvard Mark I (1944). Stroga harvardska arhitektura uporablja en naslovni prostor za programska navodila in drug ločen naslovni prostor za podatke. To pomeni, da obstajata dva ločena spomina. Sledi prikaz arhitekture:

Slika 6.71 Harvardska arhitektura

Krmilna enota izvaja dekodiranje navodil. Aritmetično logična enota (ALU) izvaja aritmetične operacije s kombinacijsko logiko (vrata). ALU izvaja tudi logične operacije (npr. prestavljanje).

Pri mikroprocesorju 6502 gre navodilo najprej mikroprocesorju (kontrolna enota), preden gre datum (ednina za podatke) v register µP, preden pride do interakcije. To zahteva vsaj dva urna impulza in ne gre za hkraten dostop do ukaza in datuma. Po drugi strani pa harvardska arhitektura zagotavlja hkraten dostop do navodil in podatkov, pri čemer tako navodilo kot podatek vstopita v µP hkrati (operacijska koda v krmilno enoto in podatek v register µP), pri čemer se prihrani vsaj en taktni impulz. To je oblika paralelizma. Ta oblika paralelizma se uporablja v predpomnilniku strojne opreme v sodobnih matičnih ploščah (glejte naslednjo razpravo).

6.7 Predpomnilnik

Predpomnilnik (RAM) je območje pomnilnika visoke hitrosti (v primerjavi s hitrostjo glavnega pomnilnika), ki začasno shranjuje navodila programa ali podatke za prihodnjo uporabo. Predpomnilnik deluje hitreje kot glavni pomnilnik. Običajno se ta navodila ali podatkovni elementi pridobijo iz nedavnega glavnega pomnilnika in jih bo verjetno kmalu znova treba. Glavni namen predpomnilnika je povečati hitrost večkratnega dostopanja do istih lokacij glavnega pomnilnika. Da bi bil dostop do predpomnjenih elementov učinkovit, mora biti bistveno hitrejši kot dostop do izvirnega vira navodil ali podatkov, ki se imenuje Backing Store.

Ko je v uporabi predpomnjenje, se vsak poskus dostopa do glavne pomnilniške lokacije začne z iskanjem predpomnilnika. Če je zahtevani element prisoten, ga procesor pridobi in takoj uporabi. To se imenuje zadetek predpomnilnika. Če je iskanje v predpomnilniku neuspešno (zgrešen predpomnilnik), je treba ukaz ali podatkovno postavko pridobiti iz podporne shrambe (glavnega pomnilnika). Med postopkom pridobivanja zahtevanega elementa se v predpomnilnik doda kopija za pričakovano uporabo v bližnji prihodnosti.

Enota za upravljanje pomnilnika

Enota za upravljanje pomnilnika (MMU) je vezje, ki upravlja glavni pomnilnik in povezane pomnilniške registre na matični plošči. V preteklosti je bilo ločeno integrirano vezje na matični plošči; danes pa je običajno del mikroprocesorja. MMU bi moral upravljati tudi predpomnilnik (vezje), ki je danes prav tako del mikroprocesorja. Vezje predpomnilnika je bilo v preteklosti ločeno integrirano vezje.

Statični RAM

Statični RAM (SRAM) ima bistveno hitrejši dostopni čas kot DRAM, čeprav na račun bistveno bolj zapletenega vezja. Bitne celice SRAM zavzamejo veliko več prostora na matrici integriranega vezja kot celice naprave DRAM, ki lahko shrani enakovredno količino podatkov. Glavni pomnilnik (RAM) je običajno sestavljen iz DRAM-a (Dynamic RAM).

Predpomnilnik izboljša delovanje računalnika, ker številni algoritmi, ki jih izvajajo operacijski sistemi in aplikacije, kažejo lokalnost referenčnega. Referenčna lokacija se nanaša na ponovno uporabo podatkov, do katerih je bil nedavno dostopen. To se imenuje časovna lokacija. Na sodobni matični plošči je predpomnilnik v istem integriranem vezju kot mikroprocesor. Glavni pomnilnik (DRAM) je daleč in je dostopen prek vodil. Referenčni kraj se nanaša tudi na prostorsko lokalnost. Prostorska lokalnost je povezana z večjo hitrostjo dostopa do podatkov zaradi fizične bližine.

Območja predpomnilnika so praviloma majhna (po številu bajtnih lokacij) v primerjavi s podporno shrambo (glavni pomnilnik). Naprave predpomnilnika so zasnovane za največjo hitrost, kar na splošno pomeni, da so bolj zapletene in dražje na bit kot tehnologija za shranjevanje podatkov, ki se uporablja v podporni shrambi. Naprave predpomnilnika se zaradi svoje omejene velikosti hitro polnijo. Če predpomnilnik nima razpoložljive lokacije za shranjevanje novega vnosa, je treba starejši vnos zavreči. Krmilnik predpomnilnika uporablja pravilnik o zamenjavi predpomnilnika, da izbere, kateri vnos predpomnilnika bo prepisan z novim vnosom.

Cilj mikroprocesorskega predpomnilnika je povečati odstotek zadetkov v predpomnilniku skozi čas in tako zagotoviti najvišjo trajno stopnjo izvajanja ukazov. Da bi dosegli ta cilj, mora logika predpomnjenja določiti, katera navodila in podatki bodo postavljeni v predpomnilnik in obhranjeni za uporabo v bližnji prihodnosti.

Logika predpomnjenja procesorja nima zagotovila, da bo predpomnjena podatkovna postavka še kdaj uporabljena, ko bo vstavljena v predpomnilnik.

Logika predpomnjenja temelji na verjetnosti, da zaradi časovne (ponavljajoče se skozi čas) in prostorske (prostorske) lokalnosti obstaja zelo velika verjetnost, da bo do predpomnjenih podatkov dostopen v bližnji prihodnosti. V praktičnih izvedbah na sodobnih procesorjih se zadetki predpomnilnika običajno pojavijo pri 95 do 97 odstotkih dostopov do pomnilnika. Ker je zakasnitev predpomnilnika majhen delež zakasnitve DRAM-a, visoka stopnja zadetkov predpomnilnika vodi do bistvenega izboljšanja zmogljivosti v primerjavi z zasnovo brez predpomnilnika.

Nekaj paralelizma s predpomnilnikom

Kot smo že omenili, ima dober program v pomnilniku navodila ločena od podatkov. V nekaterih predpomnilniških sistemih je predpomnilniško vezje na 'levi' procesorju in drugo predpomnilniško vezje na 'desni' procesorju. Levi predpomnilnik obravnava navodila programa (ali aplikacije), desni predpomnilnik pa obravnava podatke istega programa (ali iste aplikacije). To vodi do boljše povečane hitrosti.

6.8 Procesi in niti

Tako računalniki CISC kot RISC imajo procese. V programski opremi je proces. Program, ki se izvaja (izvaja), je proces. Operacijski sistem ima svoje programe. Med delovanjem računalnika se izvajajo tudi programi operacijskega sistema, ki računalniku omogočajo delovanje. To so procesi operacijskega sistema. Uporabnik ali programer lahko piše svoje programe. Ko se izvaja uporabnikov program, je to proces. Ni pomembno, ali je program napisan v zbirnem jeziku ali v jeziku visoke ravni, kot je C ali C++. Vse procese (uporabnika ali OS) upravlja drug proces, imenovan »razporejevalnik«.

Nit je kot podproces, ki pripada procesu. Proces se lahko začne in razdeli na niti, nato pa se nadaljuje kot en proces. Proces brez niti lahko štejemo za glavno nit. Procese in njihove niti upravlja isti razporejevalnik. Sam planer je program, ko je rezident na disku OS. Ko teče v pomnilniku, je planer proces.

6.9 Večprocesiranje

Niti se upravljajo skoraj tako kot procesi. Večprocesiranje pomeni izvajanje več kot enega procesa hkrati. Obstajajo računalniki s samo enim mikroprocesorjem. Obstajajo računalniki z več kot enim mikroprocesorjem. Z enim mikroprocesorjem procesi in/ali niti uporabljajo isti mikroprocesor na način prepletanja (ali časovnega rezanja). To pomeni, da proces uporablja procesor in se ustavi brez konca. Drug proces ali nit uporablja procesor in se ustavi brez dokončanja. Nato drug proces ali nit uporabi mikroprocesor in se ustavi brez dokončanja. To se nadaljuje, dokler vsi procesi in niti, ki jih je planer postavil v čakalno vrsto, nimajo deleža procesorja. To se imenuje sočasno večprocesiranje.

Če je mikroprocesorjev več kot en, obstaja vzporedno večprocesiranje v nasprotju s sočasnostjo. V tem primeru vsak procesor izvaja poseben proces ali nit, ki se razlikuje od tega, kar izvaja drugi procesor. Vsi procesorji na isti matični plošči izvajajo svoje različne procese in/ali različne niti hkrati v vzporednem večprocesiranju. Procese in niti pri vzporednem večprocesiranju še vedno upravlja razporejevalnik. Vzporedno večprocesiranje je hitrejše od sočasnega večprocesiranja.

Na tej točki se lahko bralec vpraša, kako je vzporedna obdelava hitrejša od sočasne. To je zato, ker si procesorji delijo (uporabljati jih morajo ob različnih časih) isti pomnilnik in vhodno/izhodna vrata. No, z uporabo predpomnilnika je celotno delovanje matične plošče hitrejše.

6.10 Ostranjevanje

Enota za upravljanje pomnilnika (MMU) je vezje, ki je blizu mikroprocesorja ali v mikroprocesorskem čipu. Obravnava pomnilniški zemljevid ali ostranjevanje in druge težave s pomnilnikom. Niti 6502 µP niti računalnik Commodore-64 sam po sebi nimata MMU (čeprav je v Commodore-64 še vedno nekaj upravljanja pomnilnika). Commodore-64 obravnava pomnilnik tako, da strani, kjer je vsaka stran 256 10 dolgi bajti (100 16 dolgi bajti). Ni bilo obvezno, da obravnava pomnilnik s strani. Še vedno bi lahko imel samo pomnilniški zemljevid in nato programe, ki se preprosto prilegajo v svoja različna označena območja. No, ostranjevanje je eden od načinov zagotavljanja učinkovite uporabe pomnilnika, ne da bi imeli veliko pomnilniških odsekov, ki ne morejo vsebovati podatkov ali programa.

Računalniška arhitektura x86 386 je bila izdana leta 1985. Naslovno vodilo je široko 32 bitov. Torej, skupaj 2 32 = 4.294.967.296 možen naslovni prostor. Ta naslovni prostor je razdeljen na 1.048.576 strani = 1.024 KB strani. Pri tem številu strani je ena stran sestavljena iz 4.096 bajtov = 4 KB. Naslednja tabela prikazuje strani s fizičnimi naslovi za 32-bitno arhitekturo x86:

| Tabela 6.10.1 Fizične naslovljive strani za arhitekturo x86 |

||

|---|---|---|

| Naslovi Base 16 | Strani | Naslovi Base 10 |

| FFFFF000 – FFFFFFFF | Stran 1.048.575 | 4.294.963.200 – 4.294.967.295 |

| FFFFE000 – FFFFEFFF | Stran 1.044.479 | 4.294.959.104 – 4.294.963.199 |

| FFFFD000 – FFFFDFFF | Stran 1.040.383 | 4.294.955.008 – 4.294.959.103 |

| | | | |

| | | |

| | | |

| 00002000 – 00002FFF | stran 2 | 8.192 – 12.288 |

| 00001000 – 00001FFF | stran 1 | 4.096 – 8.191 |

| 00000000 – 00000FFF | Stran 0 | 0 – 4.095 |

Aplikacija je danes sestavljena iz več kot enega programa. En program lahko zavzame manj kot stran (manj kot 4096) ali pa dve ali več strani. Tako lahko aplikacija zavzame eno ali več strani, pri čemer je vsaka stran dolga 4096 bajtov. Prijavo lahko napišejo različne osebe, pri čemer je vsaka oseba dodeljena eni ali več stranem.

Upoštevajte, da je stran 0 od 00000000H do 00000FFF

stran 1 je od 00001000H do 00001FFFH, stran 2 je od 00002000 H – 00002FFF H , in tako naprej. Pri 32-bitnem računalniku sta v procesorju dva 32-bitna registra za fizično naslavljanje strani: eden za osnovni naslov in drugi za indeksni naslov. Za dostop do lokacij bajtov strani 2 mora biti na primer register za osnovni naslov 00002 H kar je prvih 20 bitov (z leve) za začetne naslove strani 2. Preostali biti v območju 000 H na FFF H so v registru, imenovanem 'indeksni register'. Torej je do vseh bajtov na strani mogoče dostopati tako, da samo povečate vsebino v indeksnem registru od 000 H na FFF H . Vsebini v indeksnem registru se za pridobitev efektivnega naslova doda vsebina, ki se v osnovnem registru ne spreminja. Ta shema naslavljanja indeksa velja za druge strani.

Vendar program v zbirnem jeziku v resnici ni napisan za vsako stran. Za vsako stran programer napiše kodo, ki se začne od strani 000 H na stran FFF H . Ker je koda na različnih straneh povezana, prevajalnik uporablja naslavljanje indeksa, da poveže vse povezane naslove na različnih straneh. Če na primer predpostavimo, da so strani 0, stran 1 in stran 2 za eno aplikacijo in ima vsaka 555 H naslov, ki sta med seboj povezana, prevajalnik prevede tako, da ko 555 H strani 0 je treba dostopati, 00000 H bo v osnovnem registru in 555 H bo v indeksnem registru. Ko 555 H strani 1 je dostopen, 00001 H bo v osnovnem registru in 555 H bo v indeksnem registru. Ko 555 H strani 2 je dostopen, 00002 H bo v osnovnem registru, 555H pa v indeksnem registru. To je mogoče, ker je naslove mogoče identificirati z oznakami (spremenljivkami). Različni programerji se morajo dogovoriti o imenu oznak, ki se bodo uporabljale za različne povezovalne naslove.

Navidezni pomnilnik strani

Ostranjevanje, kot je opisano prej, je mogoče spremeniti za povečanje velikosti pomnilnika v tehniki, ki se imenuje 'navidezni pomnilnik strani'. Ob predpostavki, da imajo vse strani fizičnega pomnilnika, kot je opisano prej, nekaj (navodila in podatke), vse strani trenutno niso aktivne. Strani, ki trenutno niso aktivne, se pošljejo na trdi disk in jih nadomestijo strani s trdega diska, ki se morajo izvajati. Na ta način se poveča velikost pomnilnika. Ko računalnik še naprej deluje, se strani, ki postanejo neaktivne, zamenjajo s stranmi na trdem disku, ki so lahko še vedno strani, ki so bile poslane iz pomnilnika na disk. Vse to naredi enota za upravljanje pomnilnika (MMU).

6.11 Težave

Bralcu svetujemo, da reši vse težave v poglavju, preden se premakne na naslednje poglavje.

1) Navedite podobnosti in razlike računalniških arhitektur CISC in RISC. Navedite po en primer računalnika SISC in RISC.

2) a) Kakšna so naslednja imena za računalnik CISC v smislu bitov: bajt, beseda, dvojna beseda, štiri beseda in dvojna štiri beseda.

b) Kakšna so naslednja imena za računalnik RISC v smislu bitov: bajt, polbeseda, beseda in dvojna beseda.

c) Da ali Ne. Ali dvojna beseda in štiri beseda pomenita isto v arhitekturah CISC in RISC?

3 a) Za x64 se število bajtov za navodila zbirnega jezika giblje od kaj do kaj?

b) Ali je število bajtov za vsa navodila v zbirnem jeziku za ARM 64 fiksno? Če da, kakšno je število bajtov za vsa navodila?

4) Naštejte najpogosteje uporabljena navodila v zbirnem jeziku za x64 in njihov pomen.

5) Naštejte najpogosteje uporabljena navodila v zbirnem jeziku za ARM 64 in njihov pomen.

6) Narišite označen blokovni diagram starega računalnika Harvard Architecture. Pojasnite, kako se njegova navodila in podatkovne funkcije uporabljajo v predpomnilniku sodobnih računalnikov.

7) Razlikujte med procesom in nitjo ter navedite ime procesa, ki obravnava procese in niti v večini računalniških sistemov.

8) Na kratko razložite, kaj je večprocesiranje.

9) a) Pojasnite ostranjevanje kot uporabno za računalniško arhitekturo x86 386 µP.

b) Kako lahko to ostranjevanje spremenimo, da povečamo velikost celotnega pomnilnika?